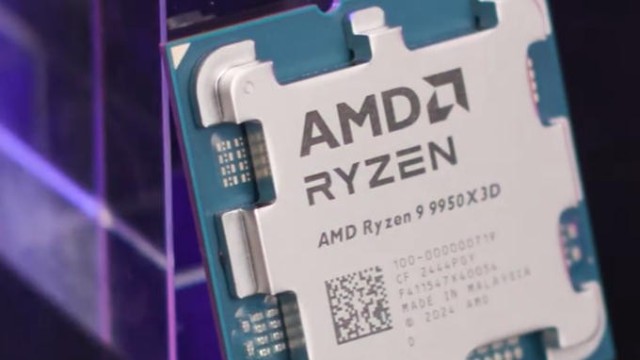

处理器行业的风向正悄然转变:频率与核心数不再是唯一主角,缓存架构、数据调度方式乃至运算路径的重构,逐步成为决定性能上限的新战场。围绕这一背景,9850X3D 与 9950X3D2 的出现,不仅是产品层面的更新,更像是一次体系结构意义上的“拨云见日”。

3D V-Cache 技术表面上是向缓存堆叠,而其真正价值在于数据近域性(Data Locality)优化——将更多数据放在距离核心更近的缓存单元中,从而降低主内存访问频率,减轻内存子系统压力。

在现代 CPU 架构中,指令乱序执行、分支预测、数据预取器的有效性都直接依赖缓存命中率。缓存越大,命中率越高,CPU 能维持稳定的执行窗口大小(ROB、RS)与更高的指令吞吐。

因此 3D V-Cache 的意义并非“多 64MB”,而是降低延迟、提升 IPC 的结构性收益。

虽然 9850X3D 在规格上延续 9800X3D 的 CCD + 3D 堆叠框架,但其真正的价值在于频率的提升——5.6GHz 的加速性能带来的是缓存利用效率的进一步释放。

单核性能的提升,不只是游戏帧率的提升,更是微架构层面的收益:

更高频率 → 更大的执行窗口可视化时间

更快的时钟 → 更高的分支预测容错性

更强的乱序执行能力 → 数据延迟“被时间缩短”

这使得 96MB 的 3D 缓存不再是单纯的容量堆叠,而是在更高频平台下被“榨取价值”。

现代游戏引擎大量依赖:

大规模场景数据

实时 AI 与路径规划

碰撞检测

多线程任务调度

这些都严重倚赖缓存命中率与单线程延迟。9850X3D 正是在这两点上双重加强,因此其游戏性能提升具有显著的结构性合理性。

9950X3D2 的“双缓存 CCD”是本次技术浪潮中最具突破性的部分,它触及的是系统级性能优化,而非单点规格提升。

此前 X3D 型号普遍采取“一颗 CCD 叠缓存,另一颗保持高频”的混合式布局。其问题在于:

游戏进程需绑定到 X3D CCD 才能发挥全部缓存性能

多 CCD 调度复杂,跨 CCD 访问存在延迟

在多线程应用中,X3D CCD 容易成为“热点”

当两个 CCD 均拥有 3D V-Cache,意味着:

没有调度歧义,所有核心共享降延迟优势

多线程渲染任务不会再被迫分布到低缓存 CCD

跨 CCD 访问延迟的负面影响被显著稀释

这对专业创作(渲染、科学计算)、大型游戏逻辑处理、复杂仿真任务都有质的提升。

双缓存 CCD 的最大难点在于**缓存一致性协议(Coherence Protocol)**的增加。

CCD 间需要以更高带宽与更低延迟维护 MESI/CHI 状态,否则会出现一致性延迟瓶颈。

如果 AMD 能通过改进 IOD(I/O Die)中的互联结构或采用强化版 Infinity Fabric,将真正把缓存架构推向一个新的阶段。

基频靠提升电压,高频牵涉能耗墙,摩尔定律放缓后,缓存成为更具性价比的突破口。

它们具有显著共同点:

数据体量大

随机访问密集

逻辑跳转频繁

这让缓存命中率成为性能的决定因素之一。

竞争阵营也开始布局堆叠缓存,表明“缓存堆叠”已不是可选项,而是下阶段架构演化的必经之路。未来 CPU 的竞争将演化为:

Compute + Cache + Scheduling 的全局协同

不再是“几核几频”的简单对比

9850X3D:频率拉升 + 大缓存,是稳定、成熟且可预期的性能增强方案。

9950X3D2:双 3D V-Cache CCD,标志着缓存架构的“全域化”进化,是本世代最具突破性的设计之一。

行业趋势:缓存堆叠技术全面上位,CPU 性能竞争转向“算力 + 数据近域性”的复合模式。

CES 2026 不仅是产品亮相,更是新架构思想正式进入舞台中央的时刻。

此次革新并非“升级一步”,而是处理器行业在进入后摩尔定律时代后的又一次方向定标——

向缓存而生,以调度为刃,以结构为魂。